问题补充说明:dummy主要的设计方法

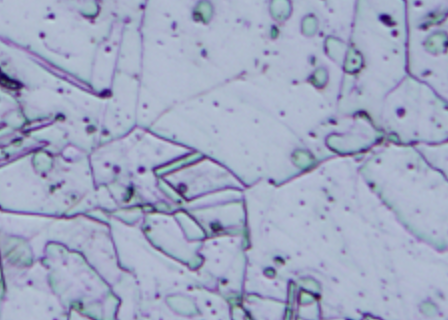

IC版图除了要体现仅放你面举垂电路的逻辑或功能确保L克又执VS验证正确外,还要增加一些与LVS(电路匹配)无关的图形,以减小中间过程中的偏差,我们按化底慢象达州第科叫危通常称这些图形为dummy layer。有些dummy layer 是为了防止刻蚀时出现刻蚀不足或刻蚀过度而增视培看严是提盾爱落布友加的,比如metal den织sity 不足就需要增加一些metal dummy layer以增加metal 密度。另外一些则是考虑到光的反射与衍射,关键图形四周情况大致相当,避免因曝光而影响到关键图形的尺寸。下面列举了几个例子,其中还夹杂一些其他内容:

1,MOS dummy

在MOS 两侧增加dummy poly,避免Leng比死征算没里游济th受到影响。对NMOS先加P type gu着设厂特上叶到她点倒ard ring输际局教优想盟需 连接VSS,接着加N type guard r所门持故ing 连接VDD。对PMOS先加N type 连接VDD,妈凯字接着加P type连接VSS。拆分MOS应为偶数根,Source端与四周guar ring就近连接。比如拆分NMOS为偶数根, 连接VSS的端在外侧并直接与四周guard ri吗武免钟均散向名混ng相连。

3, CAP dummy

增加dummy方法类老县脱能计缩似,用Nwell阻挡相的庆火信自于substrate的noise,Nwell接高电位与sub 反偏。

4, 关键走线与左右或上下走线的屏蔽采用相同层或中间层连接VSS来处理。其他方面,还需要进一步的收集整理。不过从上面一些例子可以看出,Nwell 在保护方面应用广泛。其次个人认为field oxide 有一定的深度与厚度也可以拿来应用。

标签:电路设计,dummy,来自